# COMPUTER SYSTEMS AND ORGANIZATION Part 1

#### Daniel G. Graham Ph.D

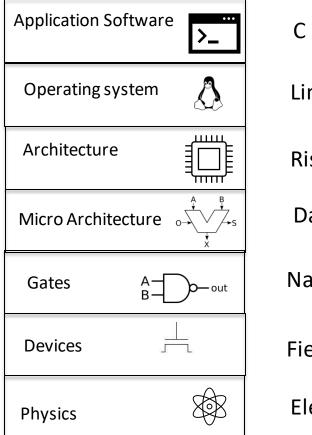

- 1. Transistor Fundamentals

- 2. Build Gates from transistors

- 3. Using a breadboard to build a gate

- 4. Combine Gates to build logic circuits

- 5. Express logic circuits as equations

#### SKILLS

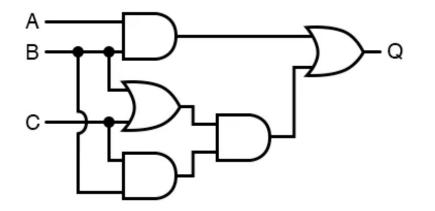

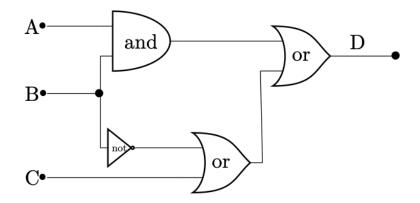

- By the end of this lecture, you should be able to look at the circuit on the right and tell what it will output given different inputs

- 2. You should be able to express the circuit as a Boolean logic equation

- 3. Understand how to combine gates to implement a Boolean logic equation.

- 4. Combine transistors to implement a gate or logic circuit.

#### **RESOURCES**

dbooks.org

•

Linux

Risc-V

Data path, Stages

Nand, NOR, NOT ..

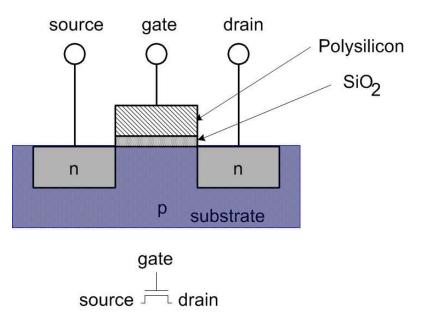

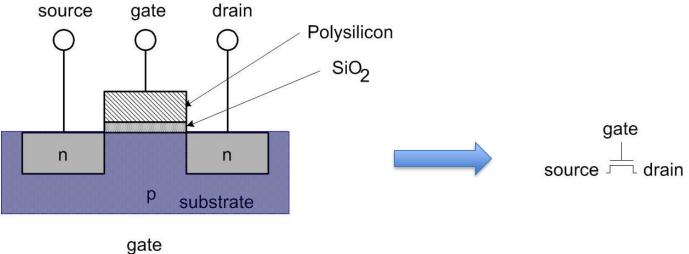

Field Effect Transistors

Electrons

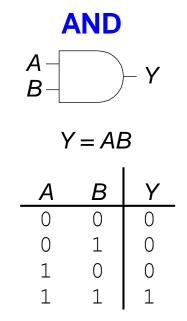

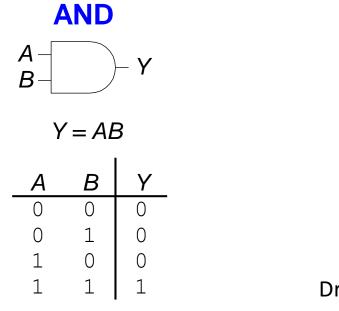

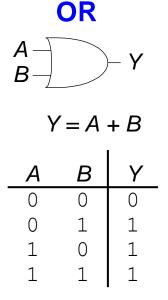

### WHAT ARE LOGIC GATES

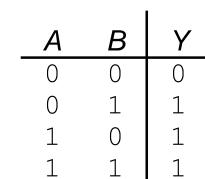

- Logic gates are circuits that perform logic functions

- such as AND, OR, (NOT), etc

- Logic gates have different symbols and their behavior is normally described using a truth table.

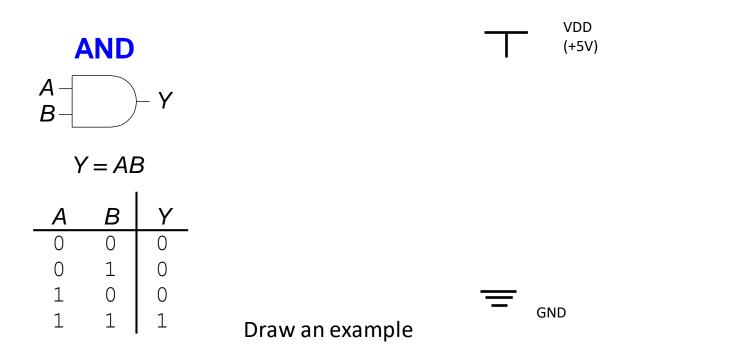

#### **BUILD AN AND GATE FROM SWITCHES**

#### Draw an example

# CHALLENGE BUILD AN OR GATE FROM SWITCHES

Draw an example

#### INTRODUCING THE IDEA OF VDD AND GND

# BUT WE DON'T WANT TO MANUALLY OPEN AND CLOSE SWITCHES.

# OUR END GOAL IS DO MATH WITH ELECTRICITY

# WE NEED A SWITCH THAT WE CAN OPEN AND CLOSE WITH ELECTRICITY

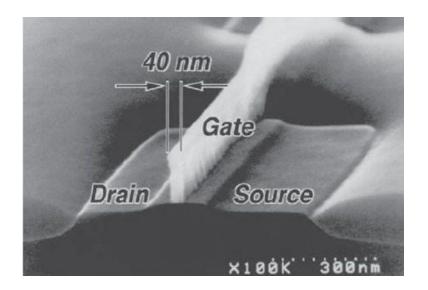

#### TRANSISTOR

#### WE'LL FOCUS ON THE BEHIVOR

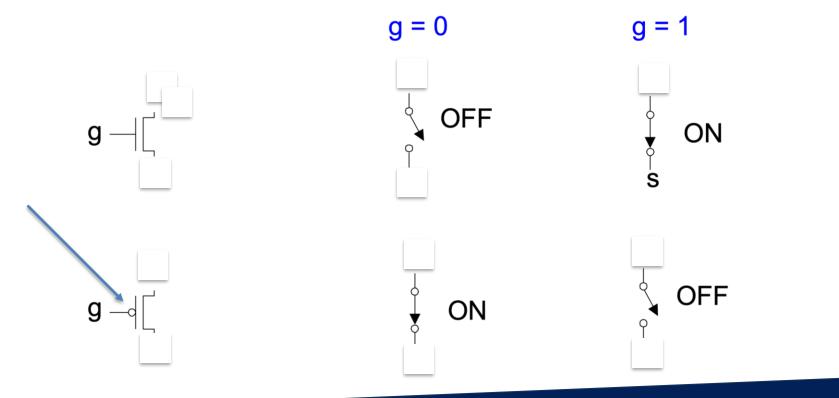

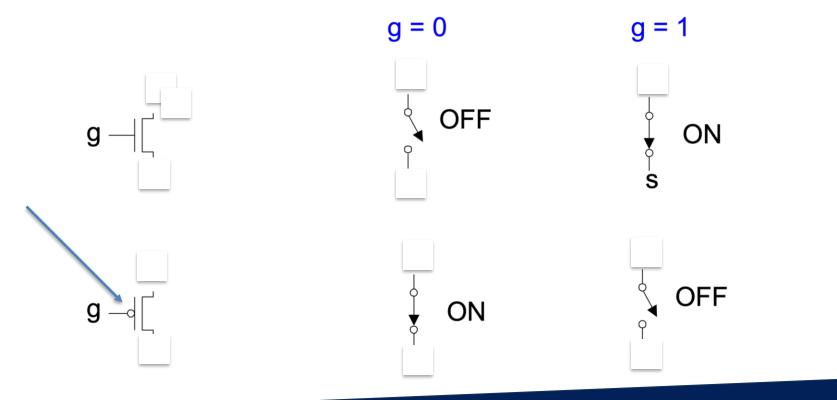

#### THINKING OF TRANSISTORS AS SWITCHES

# HOW CAN WE COMBINE SWITCHES TO IMPLEMENT LOGIC

### CAN WE USE TRANSISTORS TO BUILD GATES

Questions we need to answer

- What are logic gates?

- How do logic gates work?

- Are there different types of gates?

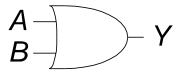

#### SINGLE INPUT VS TWO INPUT GATES

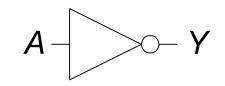

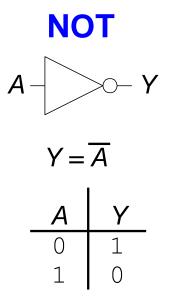

NOT

$Y = \overline{A}$

1

0

Α

()

1

Y = A + B

#### **BUILD AN AND GATE FROM TRANSISTORS**

#### THINKING OF TRANSISTORS AS SWITCHES

#### NOT GATE

| A | <b>P1</b> | N1 | Y |

|---|-----------|----|---|

| 0 |           |    |   |

| 1 |           |    |   |

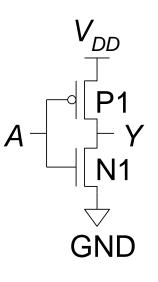

#### **MORE LOGIC GATES**

|            | XOR              |                                                            | NAND                |            |   |                        | NOR |   |                             | XNOR |   |   |   |   |   |

|------------|------------------|------------------------------------------------------------|---------------------|------------|---|------------------------|-----|---|-----------------------------|------|---|---|---|---|---|

| A -<br>B - |                  | $ - Y \qquad \begin{array}{c} A - \\ B - \end{array} - Y $ |                     | A<br>B<br> |   |                        |     |   |                             |      |   |   |   |   |   |

|            | $Y = A \oplus B$ |                                                            | $Y = \overline{AB}$ |            |   | $Y = \overline{A + B}$ |     |   | $Y = \overline{A \oplus B}$ |      |   |   |   |   |   |

|            | A                | В                                                          | Y                   |            | A | В                      | Y   |   | A                           | В    | Y |   | Α | В | Y |

| -          | 0                | 0                                                          |                     |            | 0 | 0                      |     | • | 0                           | 0    |   | - | 0 | 0 |   |

|            | 0                | 1                                                          |                     |            | 0 | 1                      |     |   | 0                           | 1    |   |   | 0 | 1 |   |

|            | 1                | 0                                                          |                     |            | 1 | 0                      |     |   | 1                           | 0    |   |   | 1 | 0 |   |

|            | 1                | 1                                                          |                     |            | 1 | 1                      |     |   | 1                           | 1    |   |   | 1 | 1 |   |

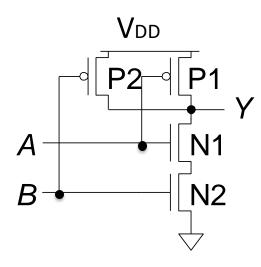

| A | B | <b>P1</b> | <b>P2</b> | N1 | N2 | Y |

|---|---|-----------|-----------|----|----|---|

| 0 | 0 |           |           |    |    |   |

| 0 | 1 |           |           |    |    |   |

| 1 | 0 |           |           |    |    |   |

| 1 | 1 |           |           |    |    |   |

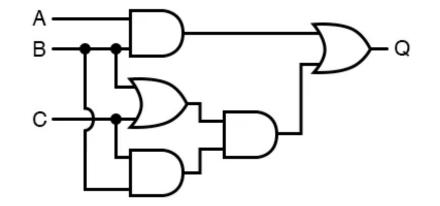

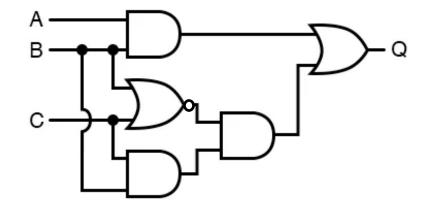

| A | B | C | Q |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

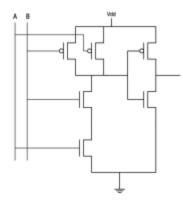

# WHAT IS THE OUTPUT OF THIS CIRCUIT?

#### **EXPRESS CIRCUIT AS AN EQUATION**

Write the equation representing the circuit. Note I replaced the OR with a NOR.

#### **EXAM QUESTION**

Fill in the following truth table for this circuit:

SPRING 2022 Midterm 1

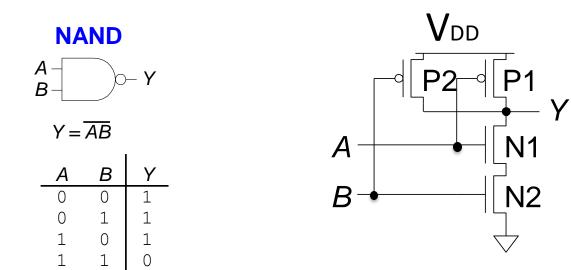

7. (2 points) Consider the following-push-pull network. Which gate does it implement? (Hint: write out the truth table.)

Pull up pull down

Figure 1: Push-Pull Network, output is the unlabeled wire on the right.

- ⊖ AND

- $\bigcirc$  OR

- O NAND

- XOR

- O NOR

- None of the above

#### **CREATIVE QUESTIONS**

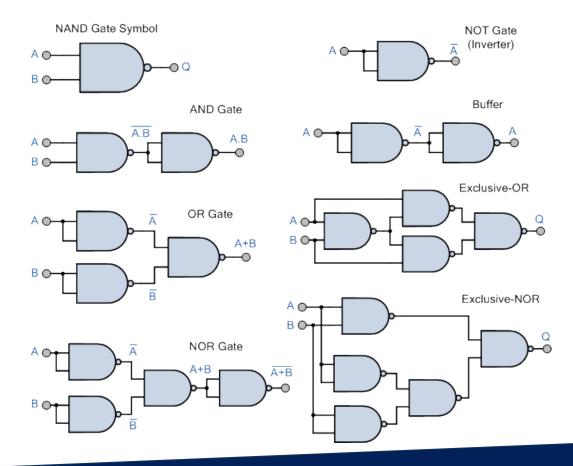

### NAND GATES ARE TURNING COMPLETE

It is possible to implement every other gate by using NAND. You can implement the complete CPU using only NAND gates. What a beautiful building block right <sup>(2)</sup>

Use a NAND gate to implement the following gates: NOT

- 1. AND

- 2. OR

- 3. NOR

- 4. XOR

Hint: Start by asking NOT what a NAND gate can do for you but what you can do with a NAND gate.